DREAM VISIO

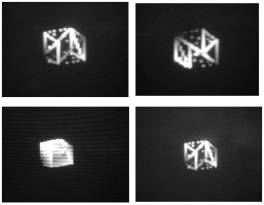

DREAM VISIO is a 3D Graphics

Processing Unit (GPU) system which incorporates a custom made CPU and a rendering engine to display

any 3D objects on the VGA. The choice of making a graphics processor was driven

by the fact that, this would be the first 3D graphics system built for this

course.

DREAM VISIO

has two main parts viz., CPU

and Rasterizer. Each 3D

object is first broken into a finite number of triangles. Our graphics system works on

these triangles to create a 3D image of the object. Normally there are many

vertices that are common between different triangles. So to reduce the time

spent in doing the geometric transforms we made our processor by working on

vertices rather than triangles. First all the geometric transforms are done on

the vertices by the CPU using its float point instructions. These vertices are

then given to the Rasterizer which renders the triangles and generates pixel

level information of each image. These rendered images are then displayed on

Monitor using the VGA module.

[Project Website of 3D GPU]

System Gimmicks And Features

|

CPU

ARCHITECTURE:

|

Basic

Type: RISC 5 stage pipeline |

|

Floating

Point Capability: yes (16-bit Format) |

|

Word

size: 16-bits |

|

Integer/Floating

Point Registers: 32 |

|

Specialized

instructions: yes |

|

Special

Arithmetic Unit: Floating Point MAC, Reciprocal |

|

Harvard

Architecture |

|

Processing

Power: 1000 vertices per second |

|

Hazard

Detection Unit: Detects all structural, data and control hazards. |

|

|

Memory Architecture:

|

Data per CPU clock

cycle: 4 words/CPU clock. |

|

Memory Speed: 12.5 MHz |

|

|

Rasterizer Organization:

|

Function: Interpolates

color and screen co-ordinates for all the pixels in triangle. |

|

Specialized Units: 8-bit

divider. |

|

Throughput: Close to 1

pixel per clock cycle. |

|

|

VGA:-

|

Aspect Ratio: 256 x 480

pixels |

|

Operating Frequency:

12.5 MHz |

|

|

Software Support:-

|

Verification for hardware implementation: Available for all modules. |

|

Assembler: yes |

|

CPU Simulator: no |

|

Rasterizer Simulator:

yes |

|

|

Device utilization summary:

|

Number

of External GCLKIOBs

1 out of 4 25%

|

| Number

of External IOBs

106 out of 166 63%

|

|

Number

of LOCed External IOBs 105 out of 106

99%

|

|

Number

of BLOCKRAMs

8 out of 28 28%

|

|

Number

of SLICEs

3131 out of 9408 33%

|

|

Number

of DLLs

1 out of 4

25%

|

|

Number

of GCLKs

3 out of 4 75%

|

|

Number

of TBUFs

122 out of 9632 1%

|

|